Sve dok su se poluvodički uređaji nalazili, motorna vozila bila su jedno od najtežih radnih okruženja. Čips u automobilima, kamionima i autobusima podložni su ekstremnim temperaturama, vlazi, vibracijama i zračenju. Izazovi dizajniranja u ovim uvjetima postajali su izraženiji s naprednim tehnološkim čvorovima, potrebnim za zadovoljavanje rastućih tržišnih zahtjeva. Ovaj članak razmatra kako testirati automobile čipove, kako tijekom proizvodnje, tako i na terenu, kako bi se osiguralo da će ispuniti očekivanja i standarde.

Ključni tržišni trendovi

U posljednjih nekoliko godina čipovi u motornim vozilima postali su među najvećim i najsloženijim u industriji poluvodiča. Napredni sustavi pomoći vozaču (ADAS) moraju integrirati širok spektar podataka senzora i analizirati ih u stvarnom vremenu. Umjetna inteligencija (AI) postaje sve važnija, čemu pridonosi razvoj tržišta autonomnih vozila. Čipovi koji kontroliraju osnovne funkcije vožnje ne smiju imati greške uzrokovane proizvodnim oštećenjima. Proizvodni testovi moraju osigurati izuzetno nisku stopu – manju od jednog neispravnog dijela na milijun (DPPM).

Osim toga, automobilski čipovi se suočavaju s izazovima izazvanim teškim uvjetima ili starenjem silicija. Greške moraju biti prepoznate i riješene na terenu, čak i kada vozila voze velikom brzinom, koristeći sustave samo-testa na čipu (BIST). Ovi sustavi moraju obuhvatiti logiku (LBIST) i memoriju (MBIST). S obzirom na visoke računalne zahtjeve AI i konkurentnu prirodu industrije, sustavi za testiranje ne smiju značajno utjecati na potrošnju energije, performanse i veličinu čipova (PPA).

Osim tehnoloških izazova, automobilski čipovi moraju zadovoljiti stroge industrijske standarde, uključujući ISO 26262 za funkcionalnu sigurnost (FUSA). Sigurnosni mehanizmi, kao što su kodovi za ispravljanje pogrešaka (ECC) i trostruka modularna redundancija (TMR), često su obavezni za detekciju grešaka u radu sustava. Sva testna logika mora pouzdano raditi čak i u ekstremnim okruženjima, što uključuje otkrivanje grešaka u vlastitoj funkcionalnosti. Također, softverska podrška FUSA osigurava da se u slučaju nepopravljive greške, vozilo zaustavi na sigurnom mjestu.

Izazovi automobilske industrije na čipovima

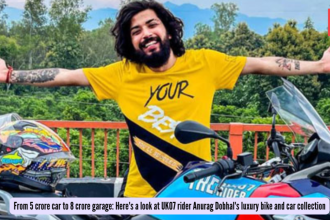

Potpuno rješenje za testiranje automobilski čipova uključuje mnoge aspekte, od kojih su neki propisani standardom ISO 26262. Ovaj standard, na primjer, definira metriku greške u jednoj točki (SPFM) te zahtijeva izračunavanje te metrike. Zadovoljavanje standarda također uključuje statičku analizu funkcionalne sigurnosti, provedenu ili na razini dizajna prenosa registra (RTL) ili na neto listi na razini vrata, što mora biti brzo kako bi se smanjio utjecaj na raspored projekta čipa. Rezultati mogu dovesti do promjena u dizajnu radi poboljšanja funkcionalne sigurnosti i sukladnosti sa standardom.

Standard zahtijeva visoku kvalitetu simulacije grešaka, s vrlo velikim šansama za otkrivanje proizvodnih nedostataka. Osim brze simulacije, ovo uključuje napredne modele grešaka koji nadmašuju tradicionalne pristupe. Da bi se otkrile sve vrste grešaka i njihovi učinci, modeli bi trebali obuhvatiti prijelaze, kašnjenja, vrijeme zadržavanja, statičko i dinamičko premošćivanje, a također i modele svjesne stanice. Prijelaz između funkcionalne simulacije i simulacije grešaka mora biti neprimjetan kako bi se izbjegli lažni alarmi.

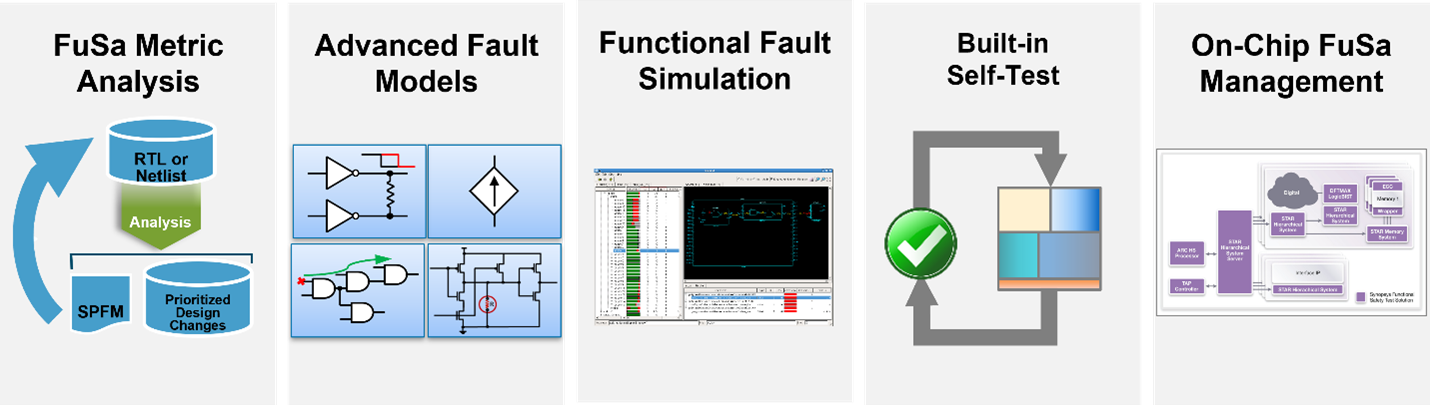

Važno je da se testne logičke strukture mogu umetati u dizajn čipa uz minimalne ručne napore. To uključuje LBIST, MBIST, ECC, sučelja procesora i mogućnosti uklanjanja pogrešaka putem testnog pristupa (TAP). S obzirom na ograničenja memorije na čipu, strukture također trebaju podržavati sveobuhvatan test vanjskog DRAM-a i visok brzinom sučelja. Mnoge od ovih funkcija mogu se implementirati putem dokazanih IP knjižnica i alata za dizajn za testiranje (DFT) koji automatski dodaju željene strukture kao dio dizajnerskog procesa.

Dokazano rješenje

Da bi se ispunili svi dosad spomenuti zahtjevi, potrebno je sveobuhvatno rješenje, koje je srećom dostupno. Obitelj automatizacije Synopsys TestMax predstavlja srce ovog rješenja. U skladu sa Synopsys VC Funkcionalnim upraviteljem sigurnosti, pruža svu analizu ispitivanja zahtijevanu ISO 26262. Izvodi DFT za umetanje testnih struktura, pokreće automatizirano stvaranje uzoraka ispitivanja (ATPG) i konvertira uzorke u formate potrebne za proizvodnju.

LBIST mogućnosti rješenja podržavaju raznolike aplikacije, uključujući:

- Test sustava na snazi (post)

- Kontroler ispitivanja u sustavu primjenjuje unaprijed programirane ili unaprijed osigurane intervale i ručke Go/no-go.

- U sistemskom testu (IS)

- Testni kontroler primjenjuje unaprijed programirane ili CPU programirane intervale i ručke go/no-go.

- Sigurnosni menadžer (CPU) programira dodatne online LBIST sekvence i upravlja njima preko testnog kontrolera ili ažuriranjem podataka u lokalnoj memoriji.

- Ispitivanje uklanjanja pogrešaka u sustavu (ISDT)

- Pristup vanjskom uređaju putem IEEE STD 1687/1500 mreža.

- Proizvodni test

- Determinističko stvaranje uzoraka skeniranja.

- Testni kontroler konfigurira IEEE STD 1500 resurse i primjenjuje podatke.

- Dodatni kanali skeniranja mogu se koristiti za povećanje propusnosti testiranja.

Rješenje dolazi sa skriptama za planiranje testa, generacije, umetanja i provjere. SMS preglednik silicija podržava post-silikonsko pokretanje, uklanjanje pogrešaka, dijagnostiku i karakterizaciju. Na kraju, Synopsys SMS IP predstavlja sveobuhvatno, integrirano rješenje za testiranje, popravak i dijagnostiku koje podržava i ugrađenu i off-chip memoriju. Ova mogućnost nadilazi samo test i dijagnozu, omogućavajući stvarno popravljanje sjećanja putem ovih sposobnosti.

Sažetak

Čipovi za automobilske aplikacije zahtijevaju visoku razinu pouzdanosti i funkcionalne sigurnosti, postavljajući visoke zahtjeve za testiranje u proizvodnji i na terenu. Synopsys TestMax predstavlja dokazano rješenje koje ispunjava ISO 26262 standarde do ASIL D (“Sigurnosno kritično”). Rješenje podržava rad u RTL fazi za omogućavanje rane validacije DFT-a i sigurnosnih mehanizama. Testiranje i sigurnost na terenu ključni su dijelovi podrške za upravljanje životnim ciklusom silicija (SLM). U današnjoj industriji ne postoji bolje rješenje za razvoj automobila s minimalnim naporima, minimalnim utjecajem na raspored i minimalnim utjecajem PPA-a, istovremeno ispunjavajući sve tržišne zahtjeve.